Опеределение

- x86 - это семейство архитектуры наборов команд, первоначально разработанные Intel на основе Intel 8086 микропроцессор и его вариант 8088.

- 8086 был представлен в 1978 году как полностью 16-битное расширение 8-битного 8080 микропроцессора Intel с сегментацией памяти в качестве решение для адресации большего объема памяти, чем может покрыть простой 16-битный адрес.

- Термин «x86» появился потому, что имена нескольких преемников процессора Intel 8086 заканчиваются на «86», включая 80186, 80286, 80386 и 80486 процессоров.

Общие сведения:

- Разработчик: Intel, AMD

- Биты: 16-бит, 32-бит и 64-бит

- Введены: 1978 (16-бит), 1985 (32-бит), 2003 (64-бит)

- Архитектура: CISC

- Тип архитектуры: регистр-память

Общие сведения:

- Переменная: от 1 до 15 байтов

- Ветвление: код условия (регистр состояния)

- Порядок байт: в основном little.

- Размер страницы: 8086 - i286 : нет. i386, i486 : страницы 4 КБ. P5 Pentium : добавлены страницы 4 МБ. (Legacy PAE : 4 КБ → 2 МБ). x86-64 : добавлены страницы 1 ГБ

Архитектура регистр-память

- Позволяет выполнять операции с памятью (или из нее), а также с регистрами

- Если архитектура позволяет всем операндам находиться в памяти, в регистрах или в комбинациях, это называется архитектурой «регистр плюс память».

- В подходе регистр – память один из операндов для операции ADD может быть в памяти, а другой - в регистре.

- Архитектура: загрузки/сохранения: оба операнда для операции ADD должны находиться в регистрах перед ADD.

- Примерами архитектуры регистровой памяти являются IBM System / 360, его преемники и Intel x86. Примеры архитектуры регистр плюс память: VAX

Регистр состояния

- Регистр, содержащий флаги, дающие дополнительную информацию о результате в процессоре

- Примеры таких регистров включают регистр FLAGS в архитектуре x86

- Отдельные биты неявно или явно считываются и / или записываются инструкциями машинного кода, выполняемыми на процессоре.

- Регистр состояния позволяет инструкции выполнять действия в зависимости от результата предыдущей инструкции.

- Обычно флаги в регистре состояния изменяются в результате арифметических операций и операций манипулирования битами. Например, бит Z может быть установлен, если результат операции равен нулю, и очищен, если он не равен нулю.

Общие флаги

- Z, Нулевой флаг: Указывает, что результат арифметической или логической операции (или, иногда, загрузки) был нулевым.

- C, Флаг переноса: Позволяет добавлять / вычитать числа, превышающие одно слово, путем переноса двоичной цифры из менее значимого слова в наименее значимый бит более значимого слова по мере необходимости.

- S/ N, Знаковый флаг. Отрицательный флаг: Указывает, что результат математической операции отрицательный.

- V/ O/ W, Флаг переполнения: Указывает, что подписанный результат операции слишком велик, чтобы поместиться в ширину регистра с использованием представления с дополнением до двух.

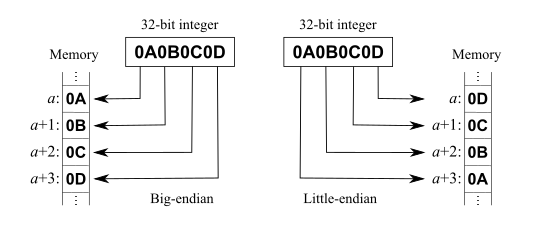

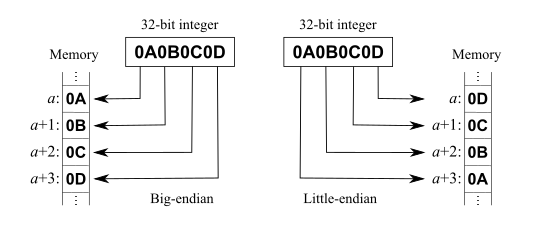

Порядок байт

- Порядок байтов - это порядок или последовательность байтов в слове цифровых данных в памяти компьютера.

- Система с прямым порядком байтов хранит старший значащий байт слова по наименьшему адресу памяти и младший значащий байт по наибольшему.

- Система с прямым порядком байтов, напротив, хранит младший байт по наименьшему адресу.

регистры x86

- Исходные Intel 8086 и 8088 имеет четырнадцать 16- битных регистров.

- Четыре из них (AX, BX, CX, DX) являются регистрами общего назначения (GPR)

- К каждому из них можно обращаться как к каждому байтам (таким образом, как к старшему байту BX можно обращаться как к BH, а к младшему - к BL).

- SP (указатель стека) указывает на «верх» стека

- BP (базовый указатель) часто используется для указания на какое-то другое место в стеке, обычно выше локальные переменные

- Регистры SI, DI, BX и BP являются адресными регистрами

- Четыре сегментных регистратора (CS, DS, SS и ES) используются для формирования адреса памяти.

- указатель инструкции (IP) указывает на инструкцию, которая будет извлечена из памяти и затем выполнена; к этому регистру нельзя получить прямой доступ (чтение или запись) для программы.

Классификация

- 1 поколение — способность исполнять код i8086 (IA16).

- 1+ поколение — частичная паралеллизация исполнения команд, специализация ФУ.

- 2 поколение — поддержка виртуальной памяти, многозадачности и 32-битности (IA32).

- 2+ поколение — L1-кэш.

- 3 поколение — встроенный FPU, исполнительный конвейер (не обязательно для RISC-подобных микроопераций).

- 3+ поколение — умножитель частоты ядра.

Классификация

- 4 поколение — IPC>=2, специализация L1.

- 4+ поколение — SIMD: 4/2/1-байтовые целые (обозначено как 4i).

- 5 поколение — конвейеризованный FPU, OoO, L2-кэш.

- 5+ поколение — IPC>=3, SIMD: вещественные одинарной (SP) и двойной (DP) точности, 8/4/2/1-байтовые целые (SP+4i и DP+8i).

- 6 поколение — многоядерность, 64-битность (x86-64).

- 6+ поколение — встроенный контроллер памяти, L3-кэш.

Правила формирования поколений

- Процессор относится к определённому поколению в том случае, если у него присутствуют все признаки этого и всех предыдущих поколений.

- Правило образования исключений: процессор может быть продвинут вперёд на полпоколения, даже если у него отсутствует требуемая функциональность, но присутствует другая функциональность более позднего поколения.

Умножитель частоты

- Множитель процессора (коэффициент умножения) — это число, на которое умножается частота шины.

- В результате получаем реальную (внутреннюю) частоту процессора.

- Например, частота шины (FSB) составляет 533 Mhz, коэффициент умножения — 4.5, получаем: 533 x 4.5 = 2398,5 Мгц.

- Почти у всех современных процессоров данный параметр является заблокированным на уровне ядра и не поддается изменению.

Расширения: модуль с плавающей точкой (FPU)

- Часть процессора для выполнения широкого спектра математических операций над вещественными числами.

- x87 — это специальный набор инструкций для работы с математическими вычислениями, являющийся подмножеством архитектуры процессоров x86.

- инструкции не являются строго необходимыми для построения рабочей программы, но будучи аппаратно реализованными, общие математические задачи они позволяют выполнять гораздо быстрее.

- Например, в наборе инструкций x87 присутствуют команды для расчёта значений синуса или косинуса.

Расширения: модуль с плавающей точкой (FPU)

- Сопроцессор подключен к шинам центрального процессора, а также имеет несколько специальных сигналов для синхронизации процессоров между собой.

- Часть командных кодов центрального процессора зарезервирована для сопроцессора, он следит за потоком команд, игнорируя другие команды.

- Центральный процессор, наоборот, игнорирует команды сопроцессора, занимаясь только вычислением адреса в памяти, если команда предполагает к ней обращение.

- Центральный процессор делает цикл фиктивного считывания, позволяя сопроцессору считать адрес с адресной шины. Если сопроцессору необходимо дополнительное обращение к памяти (для чтения или записи результатов), он выполняет его через захват шины.

- После получения команды и необходимых данных сопроцессор начинает её выполнение.

Расширения: модуль с плавающей точкой (FPU)

- Регистры FPU организованы не в виде массива, а как регистровый стек.

- FPU представляет собой стековый калькулятор, работающий по принципу обратной польской записи

- Это означает, что команды всегда используют верхнее значение в стеке для проведения операций

- Доступ к другим хранящимся значениям обычно обеспечивается в результате манипуляций со стеком

Расширения: модуль с плавающей точкой (FPU)

- Внутри FPU числа хранятся в 80-битном формате с плавающей запятой (расширенная точность)

- Вещественные числа в трёх форматах: коротком (32 бита), длинном (64 бита) и расширенном (80 бит).

- Двоичные целые числа со знаком в трёх форматах: 16, 32 и 64 бита.

- Упакованные целые десятичные числа (BCD-числа) — длина максимального числа составляет 18 упакованных десятичных цифр (72 бита).

- не-число (англ. not-a-number (NaN)). Различают два вида не-чисел.

- SNaN (Signaling Not-a-Number) — сигнальные не-числа. Сопроцессор реагирует на появление этого числа в регистре стека возбуждением исключения недействительной операции.

- QNaN (Quiet Not-a-Number) — спокойные (тихие) не-числа. Сопроцессор может формировать спокойные не-числа в качестве реакции на определённые исключения, например, число вещественной неопределённости.

Расширения: модуль с плавающей точкой (FPU)

- В FPU можно выделить три группы регистров:

- Стек процессора: регистры R0..R7. Размерность каждого регистра: 80 бит.

- Регистр состояния процессора SWR (Status Word Register) — информация о текущем состоянии сопроцессора. Размерность: 16 бит.

- Управляющий регистр сопроцессора CWR (Control Word Register) — управление режимами работы сопроцессора. Размерность: 16 бит.

- Регистр слова тегов TWR (Tags Word Register) — контроль над регистрами R0..R7 (например, для определения возможности записи). Размерность: 16 бит.

- Указатель данных DPR (Data Point Register). Размерность: 48 бит.

- Указатель команд IPR (Instruction Point Register). Размерность: 48 бит.

Расширения: модуль с плавающей точкой (FPU)

- Команды передачи данных

- Команды сравнения данных

- Арифметические команды

- Трансцендентные команды

- Команды управления

Расширения: MMX

- MMX (сокр. от MultiMedia eXtensions - мультимедийные расширения)

- набор инструкций микропроцессора, предназначенных для ускорения обработки аудио- и видеоданных.

- Технология MMX разработана компанией Intel и впервые использована в 1997 году в процессорах Pentium MMX.

- Представляет собой 57 дополнительных команд и восемь 64-битных регистров

- Позволяет процессору за одну машинную операцию обрабатывать 64-битное бинарное слово которое может включать сразу несколько более мелких однотипных "частичек" - 8 байтов (1 байт = 8 битов), 4 слова (по 16 бит) или 2 двойных слова (по 32 бита).

- За счет этого в программах, разработанных с учетом поддержки MMX, процессору для обработки большого массива однотипных данных (которыми, по сути, и являются мультимедийные данные) требуется значительно меньше времени.

Расширения: MMX

- Например, при работе с цифровым изображением с глубиной цвета 16 бит процессор с MMX, в отличие от процессора без этого набора инструкций, может одновременно обрабатывать не один, а сразу 4 пиксела.

- По результатам синтетических тестов, MMX обеспечивает в среднем почти пятикратное увеличение производительности при работе с мультимедиа. На практике эти цифры несколько скромнее - около 1,5 - 1,7 раза (в оптимизированных приложениях).

- Недостатком MMX является то, что она может быть использована процессором только для обработки целых чисел.

- Кроме того, MMX имеет общие с сопроцессором регистры, так что одновременно задействовать инструкции MMX и инструкции сопроцессора процессор не может.

Расширения: 3DNow!

- 3DNow! — технология, разработанная компанией AMD. Впервые использована в 1998 году в процессоре AMD K6-2.

- 3DNow! является развитием технологии MMX.

- Она представляет собой 21 дополнительную инструкцию процессора, предоставляющую ему возможность оперировать 32-битными вещественными числами в регистрах MMX.

- Этим 3DNow! устранила один из главных недостатков MMX, которая ограничивалась ускорением только целочисленных операций одинарной точности. 3DNow! также существенно оптимизировала работу с кешем.

- По состоянию на 1998 г. 3DNow! позволила процессорам от AMD существенно опередить конкурентов от Intel в области обработки мультимедийных данных.

Расширения: SSE

- SSE (сокр. от Streaming SIMD Extensions) – технология, разработанная компанией Intel. SIMD расшифровывается как Single Instruction Multiple Data, что значит "одна инструкция - множество данных".

- Впервые SSE была использована в 1999 году в процессорах Pentium ІІІ с ядром Katmai. Изначально она называлась KNI (Katmai New Instructions).

- SSE стала своеобразным ответом Intel на разработанную годом ранее компанией AMD технологию 3DNow!.

- Так же, как и 3DNow!, SSE применяется процессором, когда нужно совершить одни и те же действия над разными данными и обеспечивает осуществление до 4 таких вычислений за 1 такт.

- Этим достигается существенный прирост быстродействия. При этом, данные могут быть как целочисленными, так и вещественными.

- Преимуществом SSE по сравнению с 3DNow! является использование собственных регистров, благодаря чему вместе с инструкциями SSE процессор может задействовать инструкции математического сопроцессора (регистры 3DNow! являются общими с сопроцессором и использовать их одновременно процессор не может).

Расширения: SSE

- 70 новых инструкций;

- 8 (в 64-битных процессорах - 16) 128-битных регистров, каждый из которых разделён на четыре 32-битных регистра с плавающей точкой;

- одного 32-битного (в 64-битных процессорах - одного 64-битного) регистра управления, необходимого также для проверки состояния SSE инструкций.

- Каждый 128-битный регистр SSE может одновременно хранить не только 4 32-битных числа. За один такт процесор может обрабатывать любые данные, помещающиеся в 128 бит (при условии использования оптимизированного программного обеспечения).

Расширения: SSE2

- SSE2 - набор инструкций, разработанный компанией Intel и впервые использованный ею в процессорах Pentium 4 (2000 - 2001 гг.).

- По сути SSE2 является дополнением к технологии SSE, разработанной Intel в 1999 году.

- Этот набор инструкций добавил к SSE 144 новые команды (в SSE их было только 70).

- дополнительные регистры не вводились.

- инструкции SSE2 используют все те же восемь 128-битных регистров SSE и позволяют процессору улучшить работу с ними.

- В частности, SSE2 дает возможность в регистрах SSE эффективно производить разнообразные операции со скалярными и упакованными типами данных, вещественными числами

- SSE2 включает в себя сложные дополнения к командам преобразования чисел, а также алгоритмы управления кэшем процессора, минимизирующие его загрязнения при обработке объёмных потоков данных.

Расширения: SSE3

- SSE3 является развитием технологий MMX, SSE, SSE2, представляет собой набор из 13 дополнительных команд, позволяющих процессору более эффективно использовать 128-битные регистры SSE.

- инструкцию по преобразованию чисел с плавающей точкой в целые числа;

- три инструкции дублирования данных;

- инструкцию загрузки невыровненных переменных;

- две инструкции одновременного сложения/вычитания;

- четыре инструкции горизонтального сложения/вычитания;

- две инструкции синхронизации потоков.

Расширения: AVX

- AVX (Advanced Vector Extensions) - расширение системы команд процессора, разработанное компанией Intel в 2008 году, которое, как и SSE, SSE2, SSE3, SSSE3, SSE4, стало дальнейшим развитием технологий SIMD (Single Instruction - Multiple Data, то есть "одна инструкция - множество данных").

- в 2 раза были увеличены регистры SIMD (со 128 до 256 бит)

- добавлен набор дополнительных 256-битных инструкций, выполняемых в этих регистрах

- При этом, сохранилась поддержка существующих 128-битных SSE-инструкций процессора, которые теперь использовали только первую половину новых 256-битных регистров.

- Благодаря расширению регистров, процессор с поддержкой AVX за каждый такт может обрабатывать до 2 раз больше информации в интенсивных вычислениях с плавающей точкой